将8051应用程序迁移到ARM Cortex-M处理器上

Cortex-M处理器系列包括广泛使用的Cortex-M3处理器、针对FPGA的Cortex-M1 处理器、2009年初推出的Cortex-M0处理器(最小的 ARM 处理器)和2010年初推 出的 C o r tex-M4处理器(支持浮点和数字信号处理增强指令)。这些处理器具有先 进的功能特点和简单易用的编程模型,对于想从8051微控制器迁移到ARM架构的开 发人员来说,极具吸引力。本文是一篇入门指南,目的是帮助8051微控制器的开发人 员了解8051和A R M Cor tex-M处理器系列在架构、软件和硬件设计上的主要差异, 从而加快迁移过程。

架构概述

对于一些嵌入式程序员(尤其是那些习惯使用汇编语言编程的 程序员),首先要做的事情就是了解编程模型。

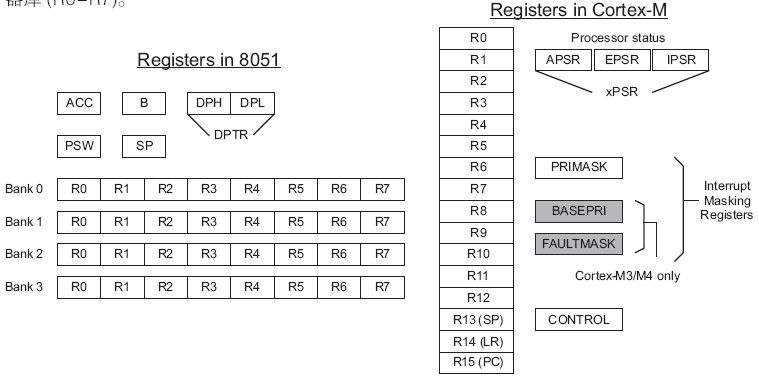

寄存器

ARM Cortex-M处理器具有一个32位寄存器库和一个xPSR(组 合程序状态寄存器)。而8051具有ACC(累加器)、B、DPTR(数 据指针)、P SW(处理器状态字)和四个各含八个寄存器的寄存 器库 (R0-R7)。

在8051中,一些指令会频繁使用某些寄存器,如ACC和 DPTR。 这种相关性会极大降低系统的性能,而在ARM处理器中,指令可

使用不同的寄存器来进行数据处理、内存存取和用作内存指针, 因此不会有这个问题。

从根本上说,ARM 架构是一个基于加载(Load)和存储(Store) 的RI S C架构,处理器寄存器加载数据,然后将数据传给A LU进 行单周期执行。而8051寄存器(ACC、B、PSW、SP和DPTR)可 在SFR(特殊功能寄存器)的内存空间中访问。

为了确保普通的C函数能够用 作中断处理程序,在需要处 理中断时,C o r t e x- M的寄存 器(R 0 - R 3、R12、L R、P C和 xPSR)会被自动压入堆栈,而软 件仅需在必要时将其他寄存器 压入堆栈。虽然8051具有4个寄 存器库,但是ACC、B、D P T R和 PSW寄存器并不会自动压栈,因 此通常需要通过中断处理程序 对这些寄存器进行软件压栈。

内存空间

ARM处理器具有32位寻址,可实现一个4GB的线性内存空间。该 内存空间在结构上分成多个区。每个区都有各自的推荐用法(虽然并不是固定的)。统一内存架构不仅增加了内存使用的灵活 性,而且降低了不同内存空间使用不同数据类型的复杂性。

相反地,8051微控制器具有多个内存空间。内存空间的分割使得 有效地利用全部内存空间变得困难,而且需要借助C语言扩展来 处理不同的内存类型。

8 0 51在外部R A M内存空间上最高支持6 4 K B的程序内存和 64K B的数据内存。理论上,可以利用内存分页来扩展程序内存 大小。不过,内存分页解决方案并未标准化,换句话说,不同 8051供应商的内存分页的实现并不相同。这不仅会增加软件开 发的复杂性,而且由于处理页面切换所需的软件开销,还会显著 降低软件性能。

在AR M C or tex-M3或M4上,S R A M区和外设区都提供了一个 1MB的位段区(bit band region)。此位段区允许通过别名地址 访问其内部的每个位。由于位段别名地址只需通过普通的内存 存取指令即可访问,因此C语言完全可以支持,不需要任何特殊 指令。而8051提供了少量的位寻址内存(内部R A M上16字节和 S F R空间上16字节)。处理这些位数据需要特殊指令,而要支持 此功能,C编译器中需要C语言扩展。

A R M C o r t ex-M处理器的内存映射包含多个内置外设块。例 如,ARM Cortex-M处理器的一个特性是具有一个嵌套矢量中 断控制器 (NVIC) 。此外,系统区中内存映射有数个指定控制寄 存器和调试组件,以确保优异的中断处理并极大方便开发人员 使用。

完整PDF文档下载

声明:本站部分内容根据互联网资料整理而成,若侵犯您的权益,请联系我们,我们会尽快处理。