LPC176x/175x 12位ADC设计指导--LPC176x/175x 12-bit ADC design guidelines

文档信息

关键字

LPC1700,LPC175X,LPC176X,12位ADC

摘要

PCB设计参考,软件测试LPC1768 12位 ADC

1.简介

基于ARM Cortex M3内核,LPC175X/6X包含一个12位模数转换模块(ADC):8引脚多路输入,转换速率达200KHZ,多个结果寄存器。此12位ADC可以和GPDMA控制器同时工作。

使用12位ADC设计系统,需要比传统的使用NXP LPC系列产品解决方案更细心。

作为对照,在10位ADC系统中使用3.3V参考电压,每一个转换值均不同于3.2mV(3.3V/1024)。在12位ADC中,LSB(最低有效位)的值低至0.8mV。对比3.2mV和0.8mV, 可以明显看出降噪技术在系统设计中有重要的作用,无论是原理图,还是PCB的设计。该应用手册,可以作为PCB板设计的指导,包含了一个参考设计和软件工程,用户可以用来测试LPC1700 12位ADC。一些测试情况也包含在里面,可以说明一些影响转换结果的因素。

2.PCB板设计参考

本文档提供了一个完整的板子设计案例。用户可以使用这个设计作为他们自己设计的起点。这个案例使用的软件叫作:Eagle布局编辑器5.4.0(Eagle Layout Editor Version 5.4.0 ),整个工程,包括原理图、布局和BOM,都在本文档中。

该板的主要目的在于ADC的测试;所有的ADC通道都能测试。两个BNC连接器,用于输入外部信号(或外部电源提供的固定电压);两个电位计,提供一个可调节的电压,可连接到模拟输入线(通过跳线选择模拟通道输入)。

这个板可以选择不同的电源。从一个通用源,就可以获得模拟或数字电源:使用USB连接器(PC供电)或者外部电源(提供3.3V外部电压)。另一种可行方案是为每一个源(模拟或数字)提供独立电源,甚至可以从一个独立的电源提供VREF(Voltage reference for the ADC,ADC基准电压)。通过跳线,用户可以选择想要的配置。

调试以及FLASH编程都有一个JTAG/SWD调试端口。通过COM0连接器(通过跳线选择相应的UART0),FLASH编程也可以使用ISP。UART1也是通过跳线选择。板上有RESET和ISP按键,一个通用LED。板上所有的GPIO引脚均可用。

板子布局与符录中的设计指导相对应。为了降低成本,采用了双层设计。底层作为接地层(ground planes)。模拟和数字接地层可用,一对跳线可以选择不同的配置。两个地端连接到一个点上,或通过一个choke相连,也有可能是自独立。这些选项可以让用户体验不同的情况,并比较结果的差异。

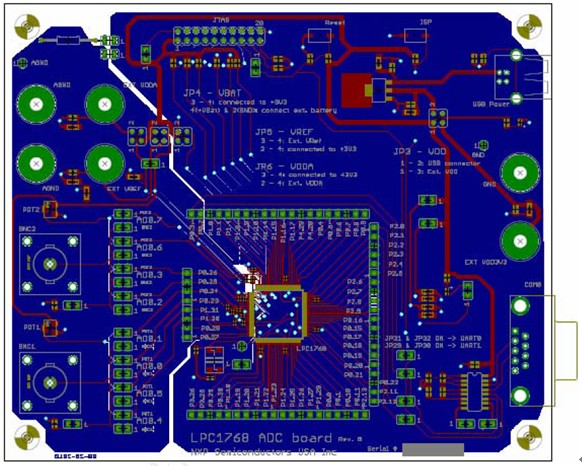

顶层主要用于电源和信号的走线(traces)。数字信号(特别是高频或者大电流部件上的)位于数字地端,远离模拟区域。模拟相关的部件(BNC连接器,模拟电位器,模拟电压的跳线和连接器)位于板的左边缘,形成一个“模拟岛”。数字相关的部件位于板的另一端。图1所示为板的最后布局。如图所示,所有的跳线都在板上注了相应的标签。

图1 LPC1768 ADC 电路板布局

3. 软件测试

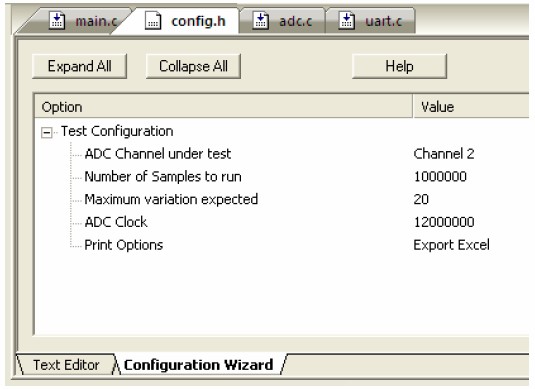

为了测试这块板,本文档提供了相应的软件。此工程使用Keil MDK version 4.03(可以使用免费的评估版本)。用这个软件,用户可以选择测试的ADC通道,以及示例的号码。其他参数,像ADC时钟,也可以设置。

理想情况下,所选择的通道输入一个固定电压时,所有的示例都会返回相同的值。实际中,可能会出现干扰或电压不稳,而导致结果出现偏差。最后的结果是出现几个接近的值,而且不会是同一个值。只要减少干扰、改进电源质量,就能把误差限定在一个较小的范围。

因为软件使用一个数列来确保不同的转换结果,所以应该先定义这个数列。代码中命名为“Maximum variation expected”的参数,作为这个数列的初始值,默认值为20,能够满足大多数情况。另两个变量限制了值的范围(最大和最小值),所以用户可以对这个参数作一些调整。

另一个参数定义了打印的选项。所有的参数都可以在config.h文件中找到,可以在Keil Configuration Wizard(Keil配置向导)中编辑,如图2所示。

图2 软件配置参数

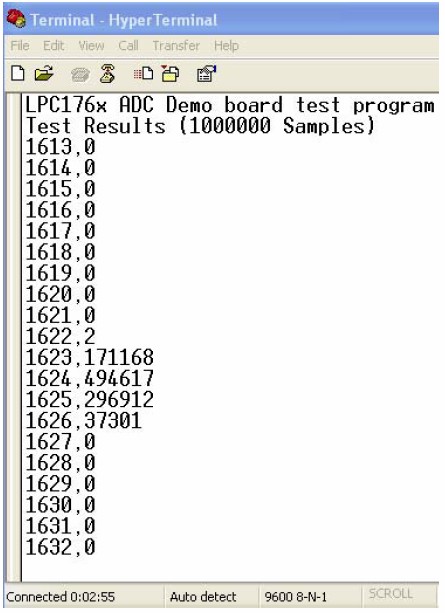

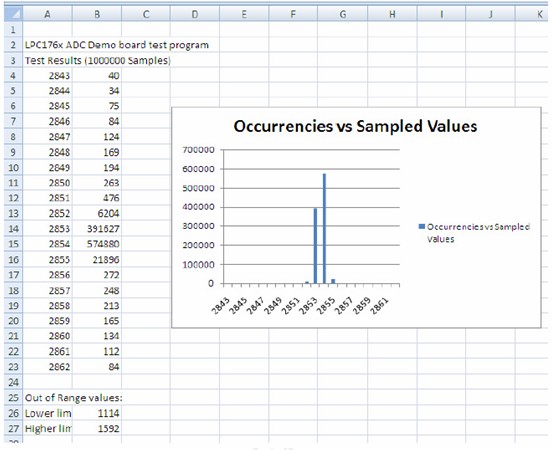

只要板编程通过,就可以通过终端程序(HyperTerminal program)查看程序的信息。使用终端,需要用串口线连接ADC板(COM0)和PC串口,启动终端程序的参数为:9600,8,N,1,N。初始化完成之后,程序启动ADC取样,结果显示在终端程序的屏幕上。如果在配置向导中选择了“Export Excel”,则取样值以及相应的序号将出现在屏幕上。见图3。

图3 终端显示的结果

获取这些信息,并保存为文件,文件后缀为“csv”。这个文件就可以用微软的Excel打开,文件上的值就会分两列显示。这样,就可以很容易的生成相应的柱形图,见图4。

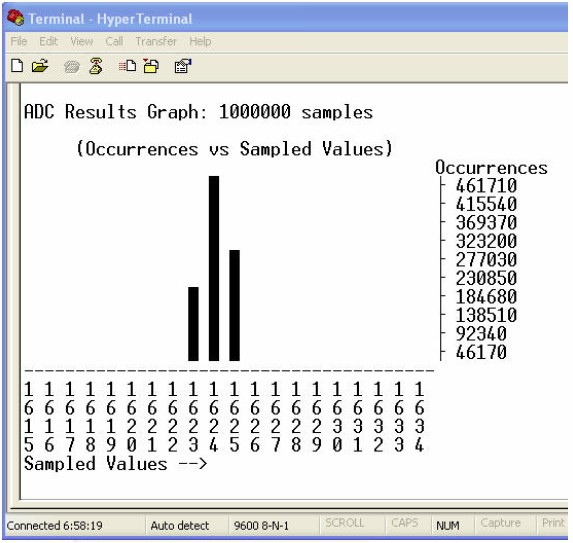

配置中的另一个打印选项“Plot Values”,结果值可以在终端屏幕上直接显示为图表,用户就可以快速评估测试结果而不需要额外的输出这些值。见图5。

注意:使用JTAG调试时会影响结果,详见4.2。

图5 终端显示柱形图

4.运行测试

在这一部分,提供了不同的测试情况,以及相应的结果。

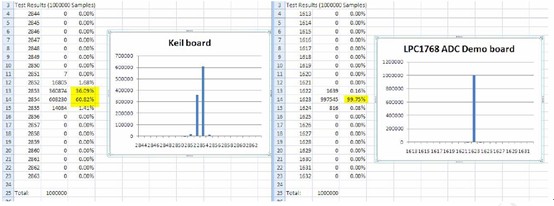

4.1 Keil MCB1700 和 LPC1768 ADC 评估板的比较

基准测试在MCB1700 Keil 板和LPC1768 ADC 评估板上进行,图六为测试结果。

如上图所示,LPC1768 ADC 评估板能够把99.75%的取样转为同一个值,干扰达到最小,由此可见,ADC的性能好于Keil板。这个结果证实了LPC1768 ADC 评估板的设计的优异性。

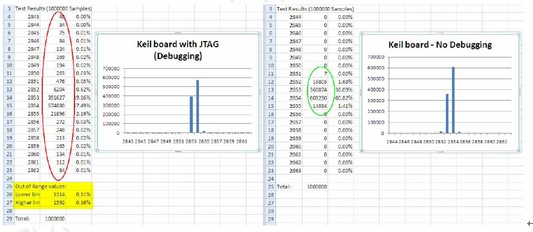

4.2 JTAG 调试的影响

提醒用户,在某些情况下,使用JTAG调试可能会对结果产生不良影响,有时会引入额外的干扰导致一些故障(值会超出范围,包括两个峰值0x000和0xfff)。图7为JTAG的影响。

图7 JTAG的影响

如图7所示,JTAG会引入额外的干扰,扩大了样值的范围。

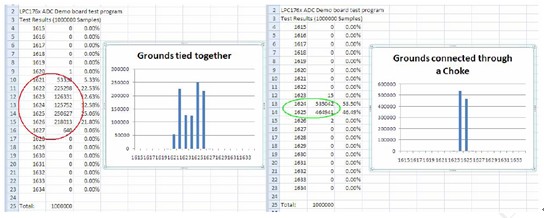

4.3 地端的影响

该板提供了两个不同的地端,一个是模拟区域,另一个是数字区域。在多数情况下,只要一个系统级的地端作为参考点,所以有时就需要把两个地端连接起来。

直接连接两个地端可能会导致数字端引入干扰到模拟区域。使用感应器(inductor)或者choke连接两个地端,由于感应器的滤波作用,数字端的干扰达到最小化,见图8。

图8 地端的影响

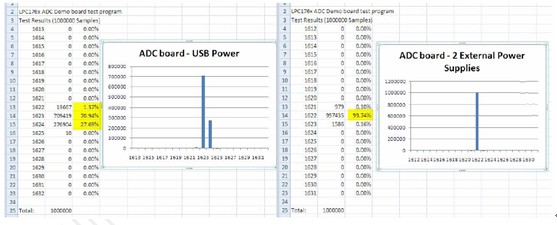

4.3 电源质量的影响

另一个干扰源就是电源。电源电压的波动,会极大的影响ADC性能。为每一块区域(数字和模拟)提供独立的电源往往能得到更好的结果,见图9。

图9 电源质量对结果的影响

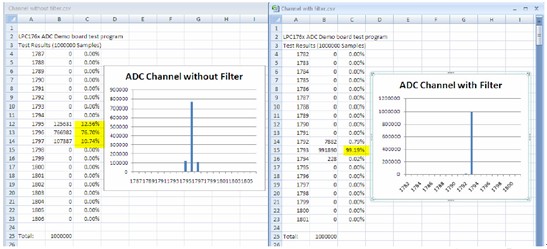

4.4 ADC通道输入滤波的影响

低通滤波器可以大大的改善结果,如图10所示。LPC1768 ADC 评估板在每一个ADC通道输入的低通滤波器上都有电容器。并不是所有板上的滤波器都起作用,这个测试显示了起作用的滤波器的改进作用。另一些情况,使用去锯齿滤波器(和相应激活的部件)能够进一步改善测试结果。

图10 低通滤波器的影响

5. 结论

设计一个精确的、可靠的12位ADC需要在PCB布局、电源设计和去耦上下功夫。PCB板的走线应该遵循本应用手册的设计原则,以减少干扰的影响。每一个区域使用一个独立的地端是一个有效的方法。如果可能,为数字和模拟区域提供独立的电源也可以获得好的结果。最后,滤波器也是一个不可或缺的部件。

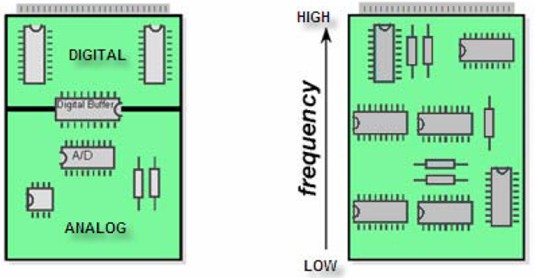

6. 附录A 设计指导

下面的指导提供了一个通用的最好的PCB布局实例:包含高频或大电流电路,模拟和数字电路相结合。

6.1 组件位置

- 模拟电路与数字电路相互独立,以隔绝转换的干扰。

- 干扰和高频组件应该布置在靠近连接器或电源的位置。

图11 推荐的组件布局

6.2 地端方案

(1)每一个区域(模拟或数字)使用独立的地端

(2)使用接地层(如果可能)

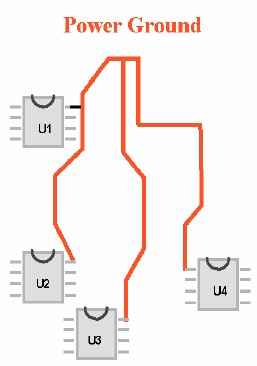

(3)如果没有接地层,地的连接使用“星”布局:

- 如果可能,使用独立的地电流回路

- 低电流/低速信号设备共用回路(参看U1&U2)

- 走线尽可能宽

- 避免地端短路

- 数字电流不要通过模拟器件

- 大电流和高速电流不要通过模拟和低速区域

- 走线尽可能的短,这样有效电感和电阻就能最小

- 如果有接地层,尽可能多使用它作为电流回路

- 为模拟部分设计独立的接地层,用空隙分离模拟和数字的接地层

- 避免板的顶部和底部可能出现的短路

- 在接地层,地电流尽可能最短;如果信号走线要插入板的接地层旁边,走线要最短,并与地电流回路相垂直。

- 当模拟和数字区域使用独立地端,则只有一个点作为系统的地,两个地端要连接在一起作为一个信号点;一个ferrite bead或感应器在这个连接部位去耦。

图12 星形布局

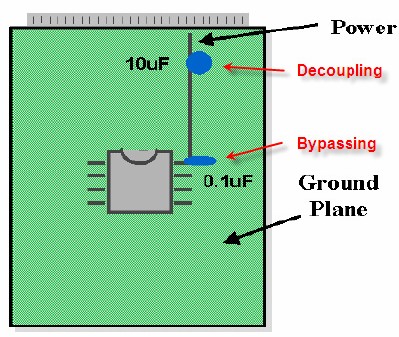

6.3 旁路和去耦电容

(1) 旁路电容为高频电流提供低阻抗通路,减少了电源线的电流干扰。通常,0.1uF就足够了,并尽可能的靠近器件。

(2) 去耦电容隔离两个电路,可以避免干扰从一个电路传到另一个电路。和一个感应器一起使用,就可以形成一个低通滤波器。10uF就可以了,且靠近电源

图13 旁路和去耦电容

6.4 电源层

(1)电源层也需要,虽然没有像接地层那么严格。

(2)两层板,电源层也可以用宽的走线代替(宽度为其他走线的2到3倍)。

6.4 多层板

(1)严格和/或复杂的设计就要使用多层板。

(2)这种情况下,强烈建议接地层和电源层使用不同层。

(3)因为很多器件都是SMD,他们的连接就需要外露在板的外部边缘;这样,内层就可以专用为电源和接地层,能够突出电容的优点。

(4)如果多于4层,接地层和电源层高速信号要隔离。低速信号要在外层上。

6.5 路由信号

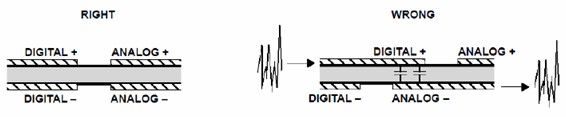

不同的区域(模拟和数字)的信号/电源/地层不要重叠。否则,电容就会把高速数字干扰加到模拟电路。

图14

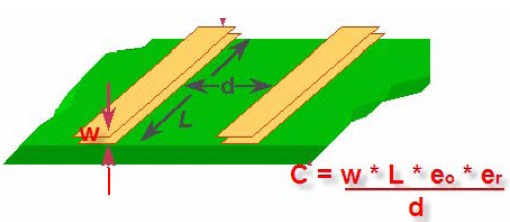

(1) 分离数字信号(特别是高频、干扰I/O、大电流)和模拟信号。即使是走线和层之间的小电容,也能引起干扰,不仅是低频,也包括高谐频。

(2) 高阻抗容易通过电容引入干扰,尤其是电压变化快的走线,像数字时钟。为了最小化电容,要加大两条走线之间的距离,且长度要长,宽度要小。

图15 推荐走线间的距离

(3) 信号走线(通常)要尽可能的短,以最小化寄生电感和电容。

(4) 避免信号线并排,以减少串扰。如果无法避免,信号线之间应该要留出至少3倍信号线宽度的间隙。

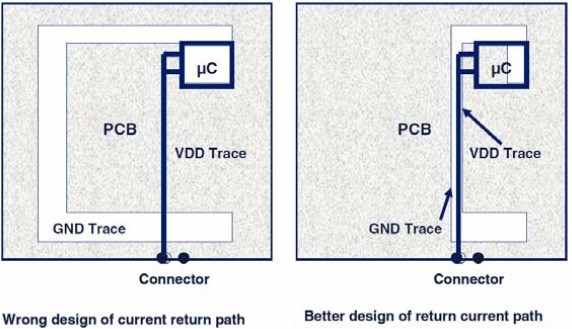

(5) 最小化电源和地走线的回路(如果没有接地端的话)。

图16

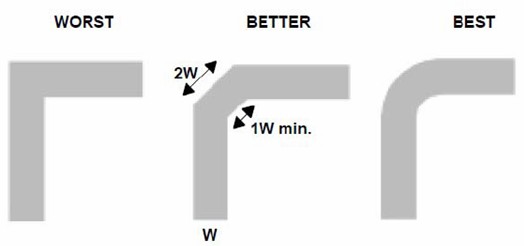

(6) 采用圆形拐角

图17 采用圆形拐角

完整PDF文档下载